FC Link Layer (LL) IP Core Overview

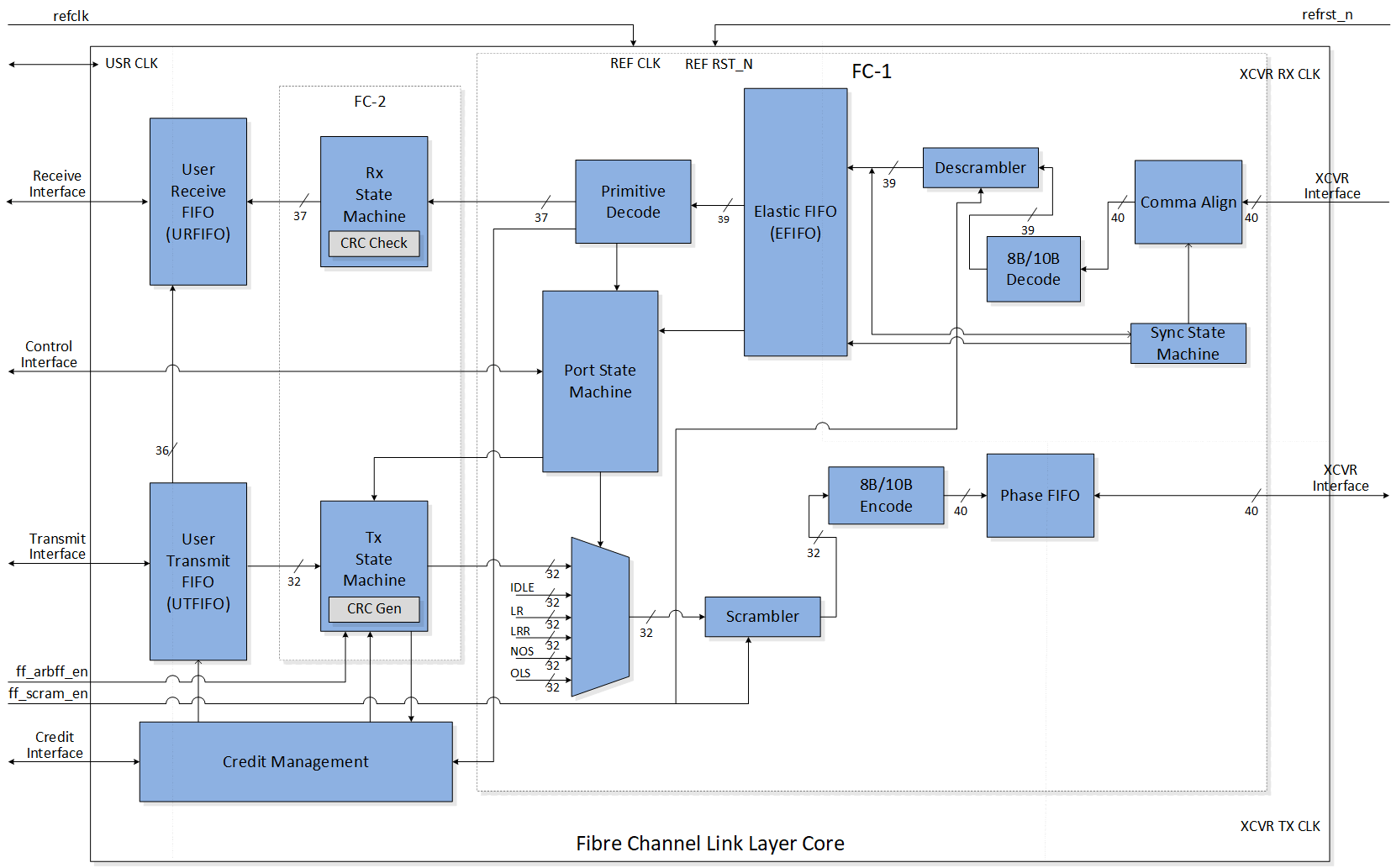

The New Wave Design Fibre Channel (FC) Link Layer core provides a complete IP solution for FC-1 and FC-2 layers. The core includes all functionality needed to meet the framing and signaling specification of Fibre Channel including: comma alignment, 8b/10b encode/decode, primitive decode, scrambling, port state machine, credit manager, CRC generation/checking, elastic FIFO, and phase FIFO.

At the physical layer, the core is built for connecting to ASIC/FPGA embedded SERDES or discrete SERDES parts. The user interface of the core provides an intuitive streaming interface for application designers. The user interface within the core also includes cross clocking logic making integration into the larger design extremely simple.

This core has been used on a diverse set of applications, from enterprise storage to aerospace electronics, and on a wide range of parts at varying operating operating rates. The core comes with test-benches and example code, making design integration a straightforward task.

Get This IP Core Pre-Loaded on the Following FPGA Cards:

PMC/XMC: V1141 (Quad-Port), V1151 (Quad-Port), V1152 (12-Port), V1153 (12-Port Rugged)

PCIe: V5051 (Quad-Port), V5052 (16-Port)

FC Link Layer (LL) IP Core Features

- Supports 1/2/4/8/16 Gbs Fibre Channel Class 3 (Class 2 optional)

- Complete FC-1 & FC-2 functionality (Switched Fabric or Point-to-Point)

- Operate in RX only, TX only, or normal RX/TX modes

- Error-injection into TX datastream to test error-detection logic

- Statistics reporting

- Real-time clock timestamping of received frames

- Stripped Mode with removal of headers and delimiters

- CRC generation and checking, 8B/10B encoding/decoding, running disparity calculation, credit management, port state machine, and FC framing

- Intuitive streaming user interface

- Scales for multiple port designs

FC Link Layer (LL) IP Core Applications

- Avionics and defense networks

- Enterprise networking/storage

- Network packet capture

- Industrial/Machine vision systems

FC Link Layer (LL) IP Core Benefits

- Accelerates FPGA application development time-to-market

- Leverage proven technology for standard interface implementation

- Lower development costs