Mil1394 GP2Lynx Link Layer Controller IP Core

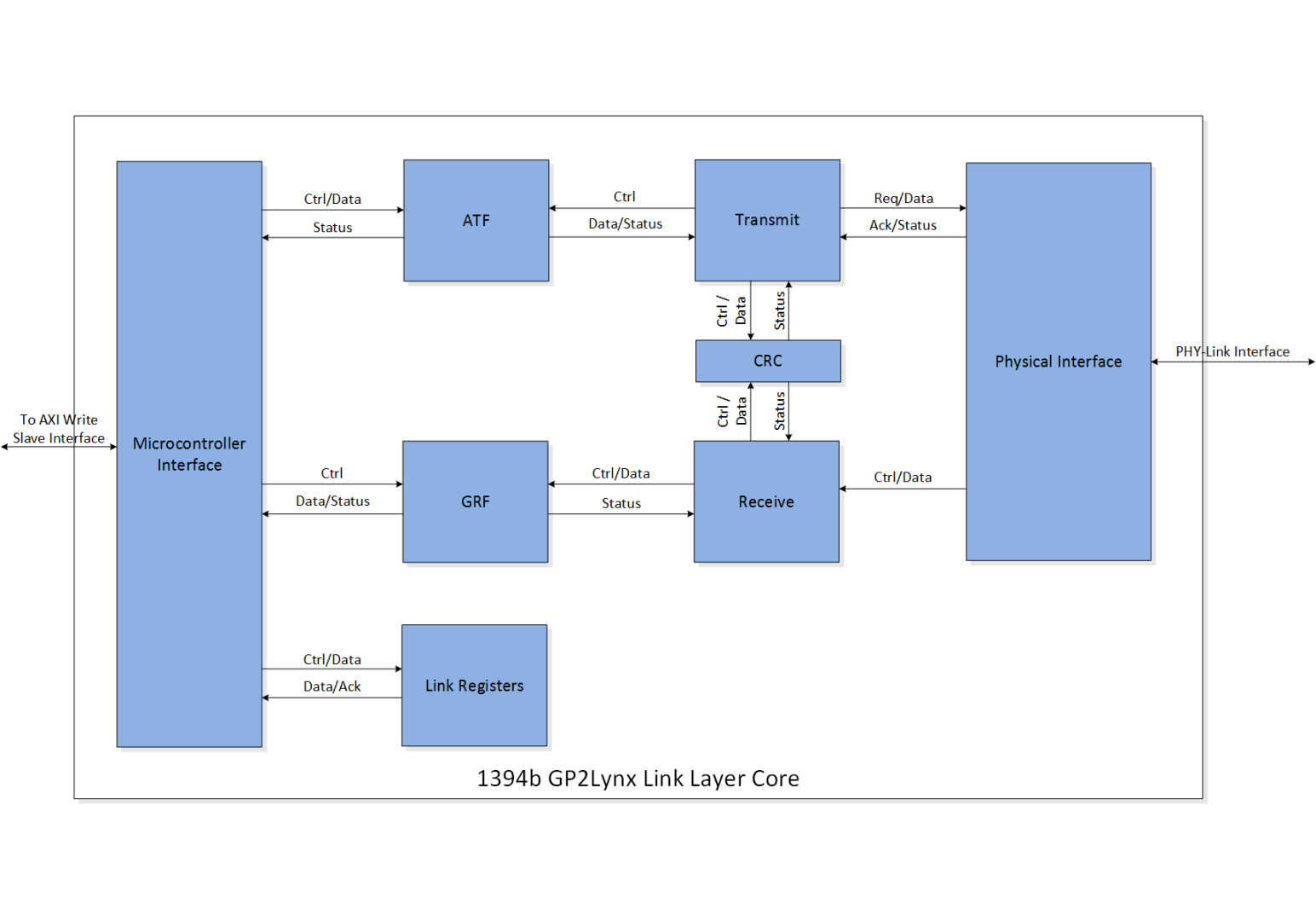

The New Wave Design 1394b GP2Lynx Link Layer IP Core provides a complete IP solution for the GP2Lynx Link Layer of the 1394 protocol.

The Core includes all functionality needed to meet the AS5643 specification including: Asynchronous Transmit, Isochronous Receive, STOF handling, STOF regulated transmit functions, and CRC generation/checking.

At the PHY-Link interface, the Core is built for connecting to any PHY implementing the defined standard PHY-Link interface. This interface is compatible with the New Wave Design PHY IP core as well as discrete PHY Layer integrated circuits.

This General Purpose IEEE-1394 Link Layer Controller (LLC) core is targeted toward aerospace and defense and has been used on a wide range of FPGAs at varying operating data rates. The Core comes with test-benches and example code, making design integration a straightforward task.

Evaluation versions of the GP2Lynx Link Layer IP Core are available and New Wave Design has a set of standard form factor boards featuring FPGAs, 1394b connectors and transformers, and off-the-shelf reference designs for quick evaluation of the IP core.

DOWNLOAD DATA SHEET REQUEST INFORMATION