Mil1394 AS5643 Link Layer Controller IP Core

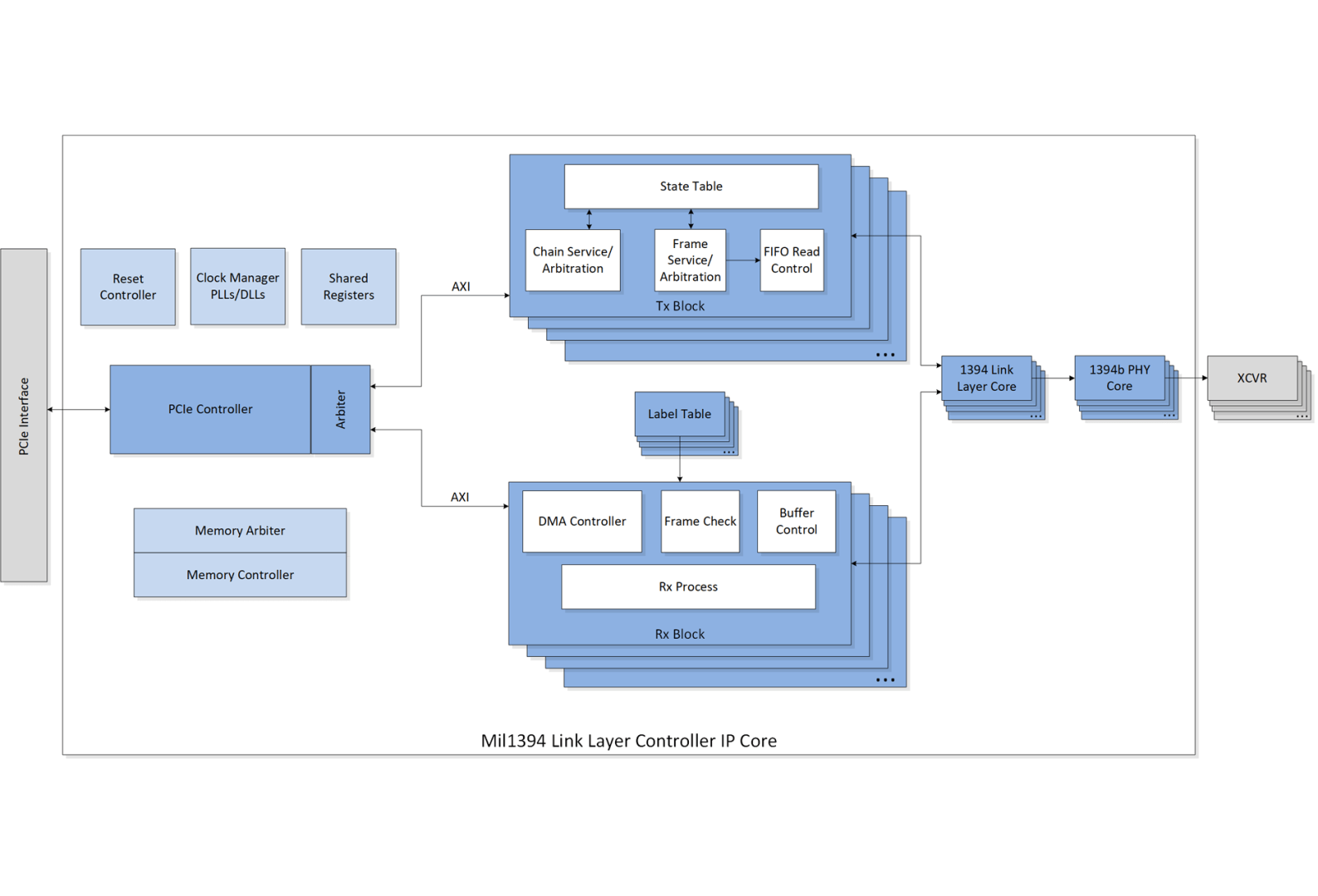

The New Wave Design Mil1394 AS5643 Link Layer Controller IP Core (Offload Engine) provides a complete hardware IP solution for the 1394 AS5643 protocol.

The Offload Engine provides hardware-based AS5643 message label filtering, hardware mapping of AS5643 message label to host memory, and complete offload of Mil1394 message handling including: Asynchronous Transmit, Isochronous Receive, STOF receive/transmit handling, STOF regulated transmit functions, Self ID operations, vertical parity, and CRC generation/checking.

The host interface to the core can be AXI or PCIe. The core is built for dropping into an FPGA and providing the complete design from processor interface to Mil1394 network interface.

This core is targeted toward applications in aerospace and has been used on a wide range of parts at varying operating rates. The core comes with test-benches and example code, making design integration a straightforward task.

Evaluation versions of the Offload Engine are available and New Wave Design has a set of standard form factor boards featuring FPGAs, 1394b connectors and transformers, and off-the-shelf reference designs for quick evaluation of the IP core.

DOWNLOAD DATA SHEET REQUEST INFORMATION