FC Upper Layer Protocol (ULP) IP Core

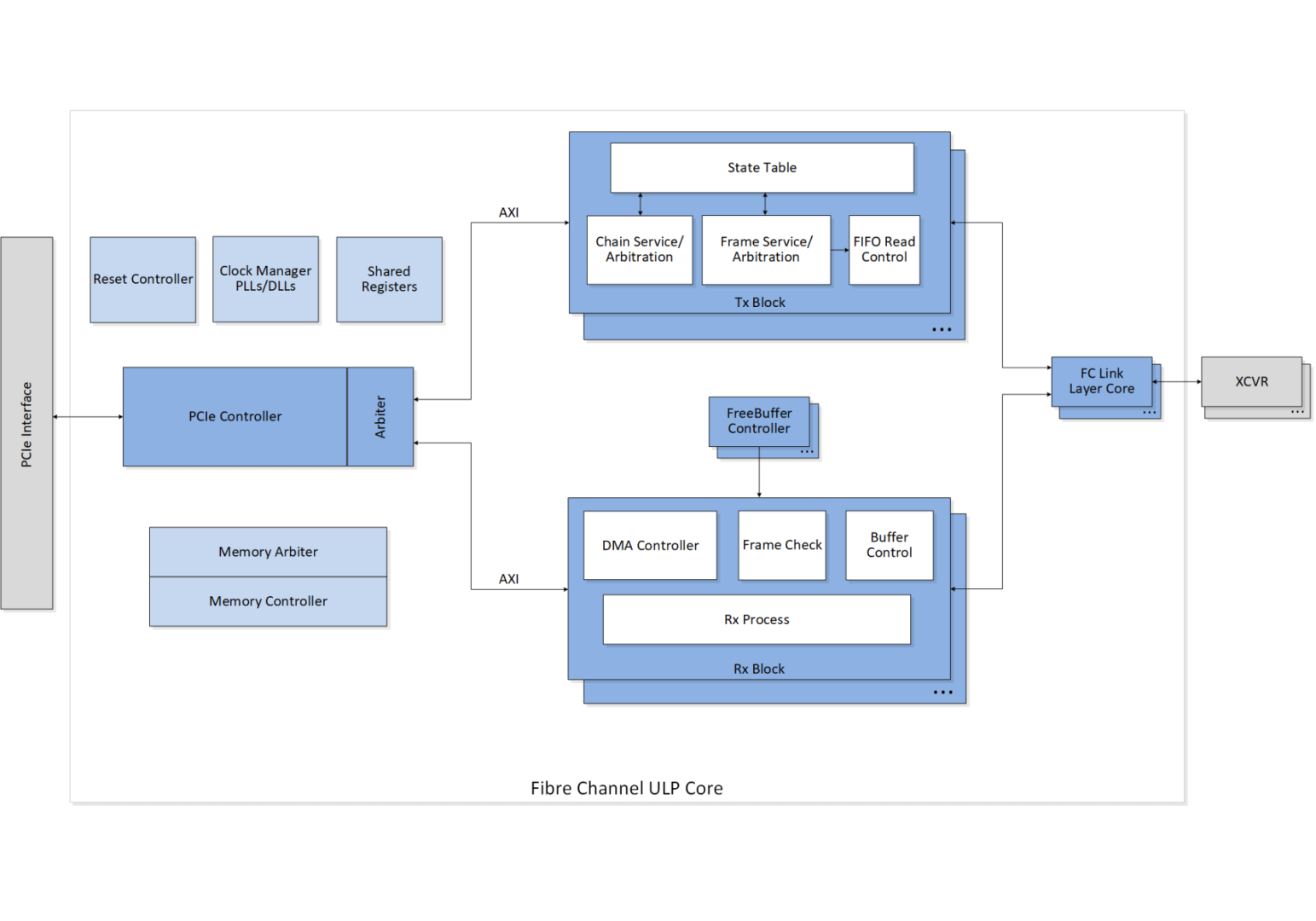

The New Wave Design Fibre Channel Upper Layer Protocol (FC-ULP) core provides a complete FC-4 layer hardware IP solution for the Fibre Channel Avionics Environment Remote Direct Memory Access (FC-AE-RDMA) and Fibre Channel Audio Video (FC-AV) protocols. FC-AE-RDMA follows the Fibre Channel Protocol for SCSI (FCP) standard.

The core provides full FC-AE-RDMA and FC-AV compliance. The host interface to the core is AXI-MM. This allows the core to be connected to an external host processor over PCIe or to an embedded SoC processor. The core is built for dropping into an FPGA and providing the complete design from processor interface to FC-ULP network interface.

This core is targeted toward applications in military/aerospace and has been used on a wide range of parts at varying operating rates. The core comes with test benches, constraints and an example design, making design integration a straightforward task.

Evaluation versions of the FC-ULP IP core are available and New Wave Design has a set of standard form factor boards featuring FPGAs, Fibre Channel optics, and off-the-shelf reference designs for quick evaluation of the IP core.

DOWNLOAD DATA SHEET REQUEST INFORMATION