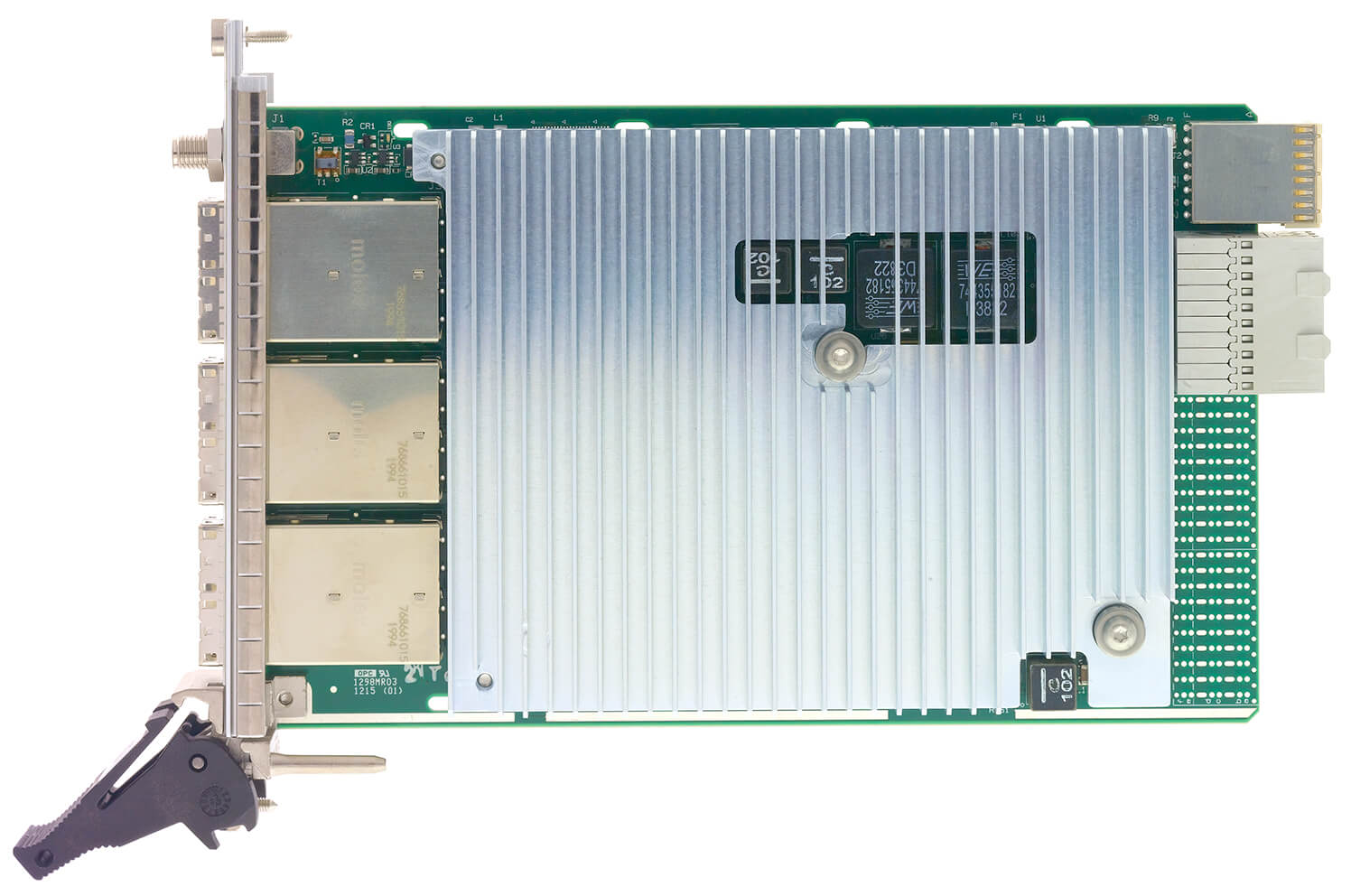

NI PXIe-7902 Ethernet Test Solution Overview

The Ethernet Test Instruments integrates up to twelve independent Ethernet interfaces into the LabVIEW™ environment using the PXIe-7902 card. The FPGA core is designed for test and verification applications and is available with LabVIEW™ support or Windows C API and can be integrated into LabVIEW™ TestStand. The Test Instrument can be operated in two modes: In interface mode, the user can control the Ethernet interfaces in real time via software. Test mode is conducted via scripted operations where the user specifies all facets of the transaction including header info, payload, packet type, and cadence/timing of operations before handing off execution to the hardware. During both modes, all incoming and outgoing packets are time stamped, recorded, and logged for user review.

See This Ethernet Test Solution in Action (VIDEO):

Testing ARINC 818 and Other High-Speed Avionics Buses w/ NI and New Wave DV (WATCH)

NI PXIe-7902 Serial RapidIO® Test Solution Features

- Fully-programmable sRIO® traffic patterns

- Hardware offload of performance critical traffic flows

- Script engine defines transaction mix, hardware executes script at wire speed

- Automatic response generation and response processing

- Hardware transmit and receive logs with time-stamping

- 512MB of on-board memory per port

- Packet Support:

- Type 2 (NREAD non-atomic)

- Type 5 (NWRITE, NWRITE_R non-atomic)

- Type 6 (SWRITE)

- Type 8 (Maintenance)

- Type 9 (Data Streaming)

- Type 10 (Doorbell)

- Type 11 (Data Message)

- User-defined Packets

- 8-bit and 16-bit DevID

- Error detection and injection

- Windows C or LabVIEW™ API and example designs

NI PXIe-7902 Serial RapidIO® Test Solution Applications

- Functional test and performance characterization of sRIO® equipment

- Emulation/simulation of sRIO® equipment and systems

NI PXIe-7902 Serial RapidIO® Test Solution Benefits

- Directly control and interface with SRIO® devices in LabVIEW™

- Configurable as host or device

- User-configurable number of lanes and lane speed at run time

- DMA access to read/write port memory

- Records and logs all transactions with hardware time-stamping

- Complete FPGA design with FPGA-based offload of protocol; No FPGA design needed by user

- Reduce development time by focusing on software test applications instead of test hardware development